# HEWLETT-PACKARD

## **JANUARY 1987**

# JOURNAL

January 1987 Volume 38 • Number 1

## Articles

4 Low-Frequency Analyzer Combines Measurement Capability with Modeling and Analysis Tools, by Edward S. Atkinson, Gaylord L. Wahl, Jr., Michael L. Hall, Eric J. Wicklund, and Steven K. Peterson Two-channel FFT analysis data can be stored directly on disc, curve fitted to find network parameters, or compared with synthesized responses.

7 Applications

**17** Measurement Modes and Digital Demodulation for a Low-Frequency Analyzer, by Raymond C. Blackham, James A. Vasil, Edward S. Atkinson, and Ronald W. Potter Swept sine and linear and logarithmic resolution modes and demodulation using digital signal processing algorithms provide greater accuracy and measurement convenience.

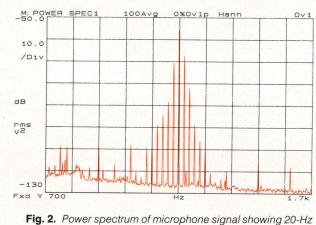

#### 22 Demodulation Example

25 Analyzer Synthesizes Frequency Response of Linear Systems, by James L. Adcock Pole-zero, pole-residue, or polynomial models can be synthesized for comparison with measured responses of low-frequency filters and closed-loop control systems.

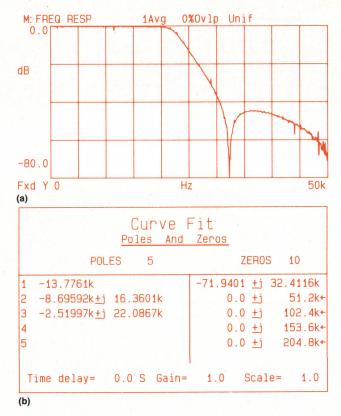

33 **Curve Fitter for Pole-Zero Analysis, by James L. Adcock** This curve fitting algorithm can derive the poles and zeros of measured frequency responses.

**38 Performance Analysis of the HP 3000 Series 70 Hardware Cache**, by James R. Callister **and Craig W. Pampeyan** State-of-the-art measurements and modeling led to improved performance.

#### **Departments**

- 3 In this Issue

- 3 What's Ahead

- 16 Correction

- 36 Authors

Editor, Richard P. Dolan

Associate Editor, Business Manager, Kenneth A. Shaw

Assistant Editor, Nancy R. Teater

Art Director, Photographer, Arvid A. Danielson Support Supervisor, Susan E. Wright

Administrative Services, Typography, Anne S. LoPresti

European Production Supervisor, Michael Zandwijken

#### In this Issue

Computers controlling instruments isn't a new story anymore, nor is built-in instrument intelligence. But few who don't use them know how very intelligent some of our electronic instruments have become. Our cover subject, the HP 3562A Dynamic Signal Analyzer, is an example of this trend. It's a measuring instrument, designed for low-frequency network and spectrum analysis, but you can use it to do computer aided design (CAD) without a computer. It not only measures and analyzes, but also synthesizes and models, all by itself—no mainframe, no workstation, no PC. With just this instrument, you can do a whole linear network design:

- Decide what shape you want the network response to have and synthesize it using the HP 3562A's built-in synthesis capabilities. The instrument will fit a rational polynomial to the response curve and compute the roots of the denominator and numerator polynomials—that is, the poles and zeros of the response. From these you can choose a network topology and component values.

- Build the prototype and measure its response in any of the analyzer's three measurement modes. Compare it with the response you wanted.

- Extract the prototype's actual poles and zeros and modify the design to get closer to the desired result.

- Repeat as necessary.

On pages 4 to 35 of this issue, the HP 3562A's designers explain how it works and what it can do. Its basic functions are described in the article on page 4, and the details of its measurement modes are in the article on page 17. Unusual is the analyzer's digital demodulation capability. Give the analyzer a modulated carrier, and if the modulation is within its frequency range, it can extract and analyze it. It doesn't matter if you don't know the carrier frequency or whether the modulation is amplitude, phase, or a combination (as long as the two modulating waveforms don't have overlapping spectra). The article on page 33 reveals the theory of operation of the curve fitter and tells how so much computing power was made to fit in the available memory. The article on page 25 walks us through several examples of the use of the HP 3562A to solve realistic analysis and design problems.

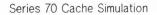

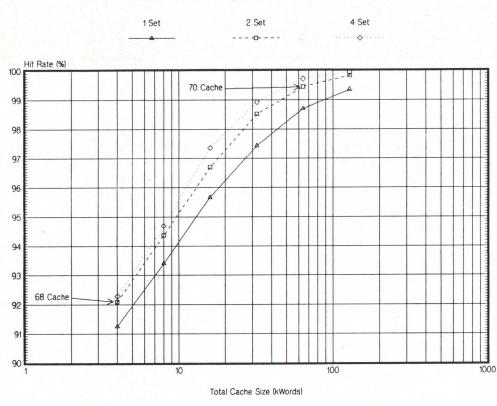

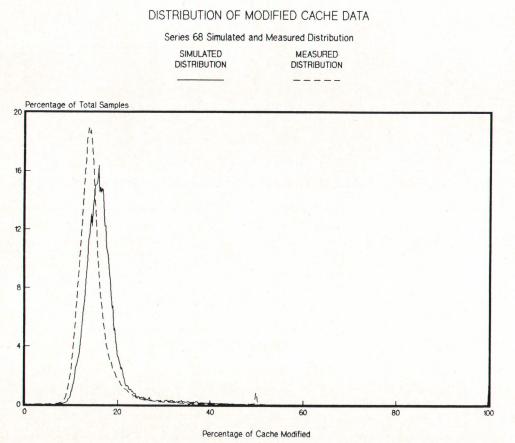

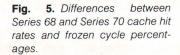

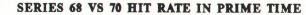

The HP 3000 Series 70 Business Computer is the most powerful of the pre-HP-Precision-Architecture HP 3000s. The objective for its design was to upgrade the Series 68's performance significantly in a short time. Measurement, modeling, and verification were used to identify and evaluate possible design changes. The paper on page 38 describes the methods and how they were applied to the Series 70's cache memory subsystem, its major improvement. According to the authors, the design of a cache provides a severe test for any estimation methodology. They feel they have advanced the state of the art in cache measurement and prediction.

-R. P. Dolan

#### Cover

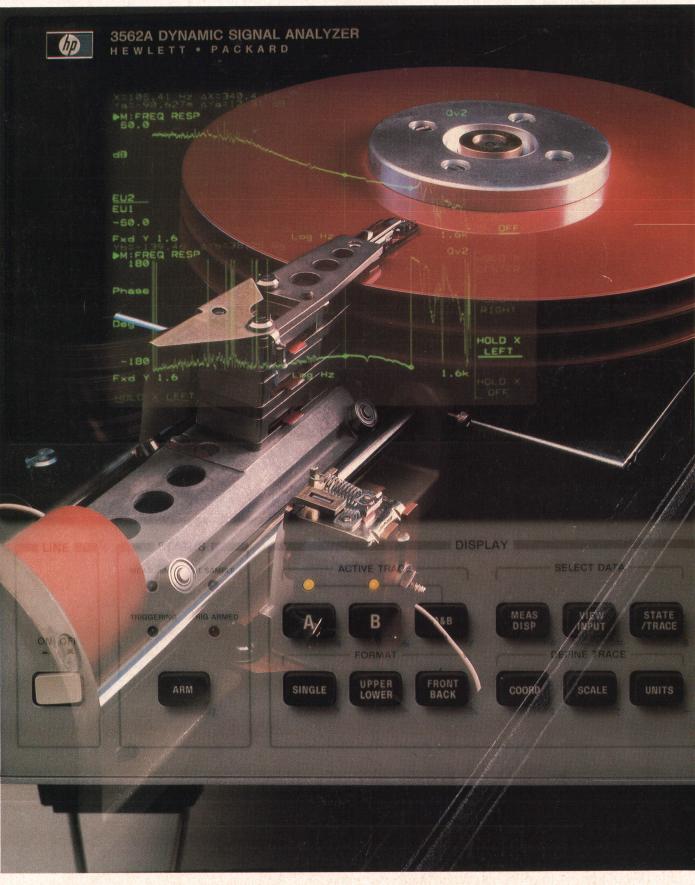

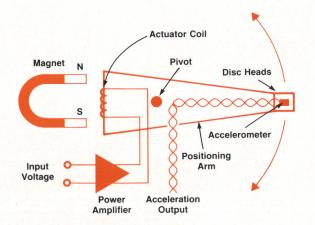

A principal use of the HP 3562A Analyzer is the design of servo systems such as the head positioning mechanisms for disc drives.

#### What's Ahead

The February issue will feature several articles on the design of a new family of fiber optic test instruments. The family includes three LED sources, an optical power meter with a choice of two optical heads, two optical attenuators, and an optical switch. Microwave transistor measurements using a special fixture and de-embedding techniques will also be treated.

The HP Journal encourages technical discussion of the topics presented in recent articles and will publish letters expected to be of interest to our readers. Letters must be brief and are subject to editing. Letters should be addressed to: Editor, Hewlett-Packard Journal, 3200 Hillview Avenue, Palo Alto, CA 94304, U.S.A.

# Low-Frequency Analyzer Combines Measurement Capability with Modeling and Analysis Tools

HP's next-generation two-channel FFT analyzer can be used to model a measured network in a manner that simplifies further design.

### by Edward S. Atkinson, Gaylord L. Wahl, Jr., Michael L. Hall, Eric J. Wicklund, and Steven K. Peterson

HE NAME FFT ANALYZER has been applied to a category of signal analysis instruments because their dominant (in some cases, their only) analysis feature has been the calculation of the fast Fourier transform of the input signals for spectrum and network response measurements. These analyzers produce an estimate of a network's frequency response function at equally spaced frequency intervals.

These FFT analyzers have justified their use for low-frequency signal analysis mainly because of their higher measurement speed when compared to conventional swept frequency response analyzers. However, proponents of swept sine analyzers are quick to point out their instruments' wider dynamic range and ability to characterize nonlinearities in a network. Proponents of 1/3-octave analyzers jump into the fray by extolling the advantages of logarithmically spaced spectrum analysis. These debates about which is the "best" analyzer can never really be won, since, in reality, all of these measurement techniques have their advantages depending on the application.

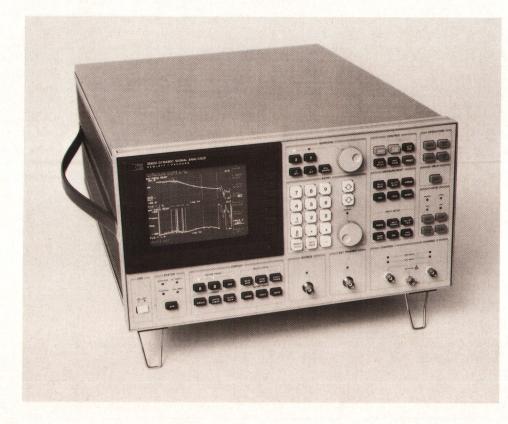

This fact was recognized in the design of the HP 3562A Dynamic Signal Analyzer (Fig. 1), which provides three different measurement techniques for low-frequency analysis within one instrument:

- FFT-based, linear resolution spectrum and network analysis

- Log resolution spectrum and network analysis

- Swept sine network analysis.

These measurement techniques use advanced digital signal processing algorithms that result in more accurate and more repeatable measurements than previously available with conventional analog implementations.

Fig. 1. The HP 3562A Dynamic Signal Analyzer performs fast, accurate network, spectrum, and waveform measurements from dc to 100 kHz. Measurements include power spectrum, histogram, frequency response, and crosscorrelation. These can be performed in real time or on stored data. Built-in analysis and modeling capabilities can derive poles and zeros from measured frequency responses or construct phase and magnitude responses from user-supplied models. Direct control of external digital plotters and disc drives allows easy generation of hard copy and storage of measurement setups and data.

The HP 3562A has two input channels, each having an overall frequency range from 64  $\mu$ Hz to 100 kHz and a dynamic range of 80 dB.

#### **Measurement Modes**

**Linear Resolution.** In the linear resolution (FFT) mode, the HP 3562A provides a broad range of time, frequency, and amplitude domain measurements:

- Frequency domain—linear spectrum, power spectrum, cross spectrum, frequency response, and coherence functions

- Time domain—averaged time records, autocorrelation, cross-correlation, and impulse response functions

- Amplitude domain—histogram, probability density function (PDF), and cumulative distribution function (CDF).

A special feature in the linear resolution mode is the ability to perform AM, FM, or PM demodulation on each input channel. Traditionally, demodulation has been performed using separate analog demodulators whose outputs are connected to the test instrument. The digital demodulation technique in the HP 3562A has the advantages of higher accuracy and greater dynamic range than analog demodulation, and it is built into the test instrument.

The type of demodulation is independently selectable for each channel. For example, a frequency response measurement can be performed using AM demodulation on Channel 1 and PM demodulation on Channel 2. As another example, a two-channel power spectrum measurement can be set up in which AM demodulation is specified for Channel 1 and no demodulation is selected for Channel 2. One can easily perform two types of demodulation (e.g., AM and FM) simultaneously on the same input signal by connecting it to both channels.

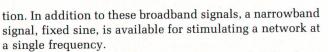

A preview mode allows the user to view (and modify) the modulated input signal before the demodulation process is invoked. There is also a special demod-polar display that shows the locus of the carrier vector as its amplitude and phase vary for AM and PM signals. This display is very useful for observing possible interrelationships between AM and PM signals.

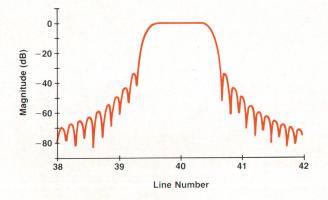

Log Resolution. In many applications, the network or signals of interest are best characterized in terms of logarithmic or proportional frequency resolution. The HP 3562A provides a true proportional resolution measurement—not simply a linear resolution measurement displayed on a log frequency scale.

In this mode, the user can make the following frequency domain measurements: power spectrum, cross spectrum, frequency response, and coherence functions. For log resolution measurements, the average quantity is always a power quantity. Stable, exponential, and peak hold averaging modes are available and offer the same benefits as in the linear resolution mode.

The user can select a frequency span from one to five decades with a fixed resolution of 80 logarithmically spaced spectral lines per decade. For example, if the start frequency is set to 1 Hz and the span is set to five decades, the frequency range of the measurement will be from 1 Hz to 100 kHz with 400 lines of resolution. Both random noise and fixed sine source outputs are available in this mode. **Swept Sine.** When swept sine mode is selected, the HP 3562A is transformed into an enhanced swept frequency response analyzer. In this mode the user can make the following frequency domain measurements: power spectrum, cross spectrum, frequency response, and coherence functions. The user can select either linear or log sweep with a full range of sweep controls, including sweep up, sweep down, sweep hold, and manual sweep. During the sweep, the HP 3562A's built-in source outputs a phase-continuous, stepped sine wave across the selected frequency span and a single-point Fourier transform is performed on the input signal.

There are four key setup parameters associated with the sweep for which the user can either set fixed values or specify an automatic mode of operation. These parameters are input range, integration time, source output gain, and frequency resolution.

By judiciously selecting these automatic sweep features, the user can perform a measurement in which the sweep adapts dynamically to meet the requirements of the device under test.

A discussion about the technical basis behind the HP 3562A's measurement modes and digital demodulation capability is given in the article on page 17.

#### **Advanced Data Acquisition Features**

Normally, measurements are made on-line using the data currently being acquired from the input channels. However, the HP 3562A provides two modes in which data can be acquired and then processed off-line at a later time.

**Time Capture.** In this mode, up to ten time records (20,480 sample points) from either channel can be stored in a single buffer. This data can be acquired in real time for any frequency span up to 100 kHz. The user can display a compressed version of the entire time buffer or any portion of it in the time or frequency domain. Furthermore, the time capture buffer can be used as an input source for any of the single-channel measurements available in linear resolution mode.

If a measurement is set up with the same frequency range as the time capture data, then up to ten averages can be done. At the other extreme, a measurement with one average can be made with a frequency span that is a factor of 10 narrower than the original time capture frequency range. For example, if a time capture is performed with a span from dc to 10 kHz, the user can perform a power spectrum measurement on this data within a 1-kHz span centered anywhere from 500 Hz to 9.5 kHz. Several display options (e.g., expansion, scrolling, etc.) are available for manipulating time capture data.

**Time Throughput.** The HP 3562A is special among low-frequency analyzers in offering the capability to throughput time data directly from the input channel(s) to an external disc drive. No external HP-IB (IEEE 488/IEC 625) controller is needed for this operation.

The instrument can throughput data to an HP CS/80 hard disc drive (e.g., the HP 7945) at a real-time measurement span of 10 kHz for single-channel operation and 5 kHz for dual-channel operation. The throughput data session can be used as an input source for both linear resolution (including demodulation) and log resolution measurements. As in the time capture mode, zoomed measurements can be made on real-time throughput files. However, much narrower zoom spans are possible since a throughput file can be much larger than the internal time capture buffer.

The user can conveniently view the data in the throughput file by stepping through the file one record at a time. Measurements do not have to start at the beginning of the file—an offset into the file can be specified for the measurement start point.

#### Modeling and Data Analysis Capabilities

Given the extensive measurement capability described above, the design of the HP 3562A could have stopped there—as a versatile test instrument. However, combining this measurement performance with equally extensive built-in analysis and design capabilities turns the product into a one-instrument solution for many applications.

**Flexible Display Formats.** Generally, the result of a measurement process is the data trace on the screen. Graphical analysis is simplified by the HP 3562A's full complement of display formats. The independent X and Y markers (both single and band) and the special harmonic and sideband markers make it easy to focus on important regions of data. The annotated display and the special marker functions (e.g., power, slope, average value, THD, etc.) allow simple quantitative analyses to be performed directly on the displayed data.

**Waveform Calculator.** The instrument includes a full complement of waveform math functions including add, subtract, multiply, divide, square root, integrate, differentiate, logarithm, exponential, and FFT. The operands (either real or complex) for the math functions can be the displayed trace(s), saved data traces, or user-entered constants. A powerful automath capability allows the user to specify a sequence of math operations to be performed on any of the standard data traces while the measurement is in progress. The user's custom measurement result can then be displayed at any time by simply pressing the automath softkey, which can be relabeled to indicate the name of the function. Some examples include group delay, Hilbert transform, open-loop response, and coherent output power (COP). Automath is discussed in more detail later in this article.

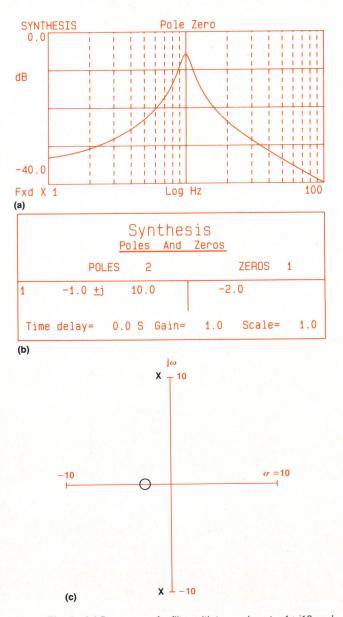

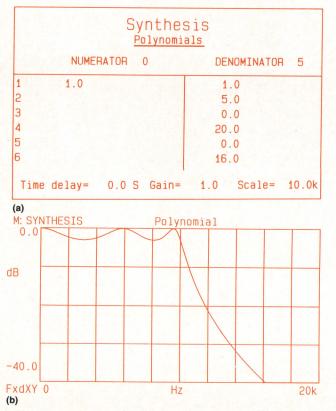

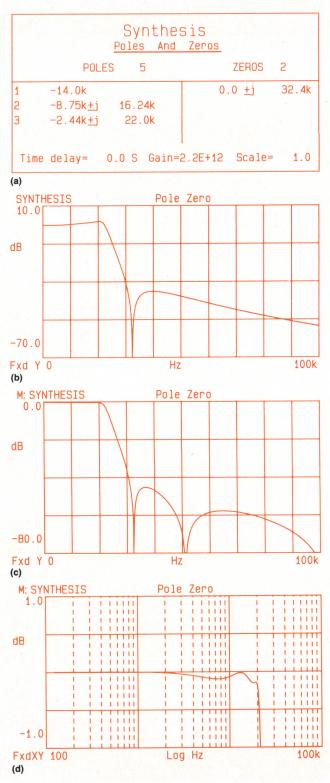

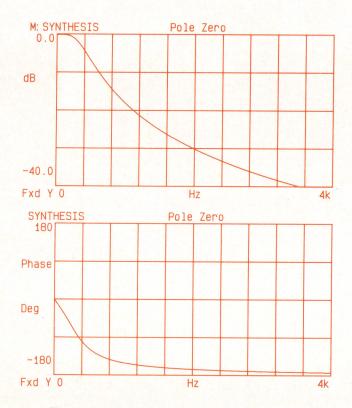

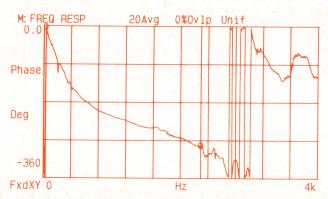

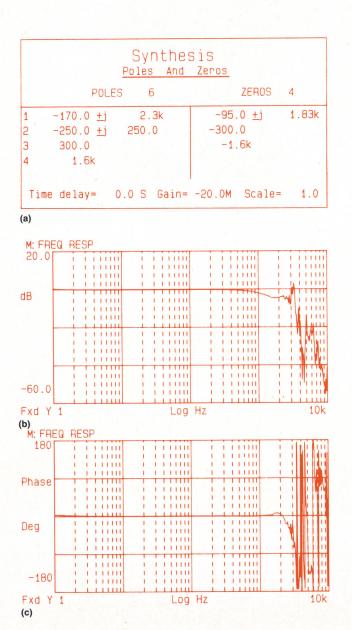

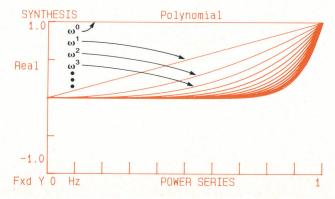

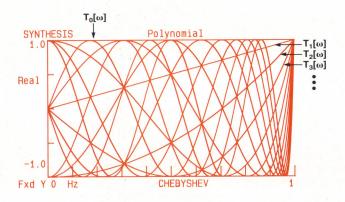

**S-Plane Calculator.** The HP 3562A can synthesize frequency response functions from either pole-zero, pole-residue, or polynomial coefficient tables. In addition, the user can convert from one synthesis table format to another with a single keystroke. As an example, a designer can enter a model of a filter in terms of numerator and denominator polynomial coefficients and then convert to pole-zero format to find the roots of the polynomials. This s-plane calculator is a powerful network modeling tool and it exists within the same instrument that will be used to test and analyze the actual network—providing on-screen comparison of predicted and measured results. See the article on page 25 for more details about the HP 3562A's synthesis capabilities and some design examples.

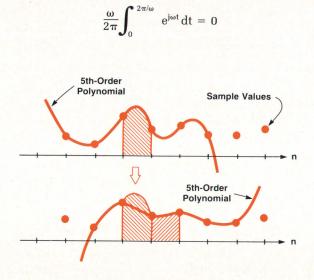

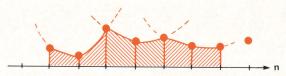

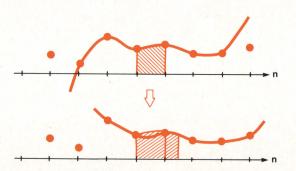

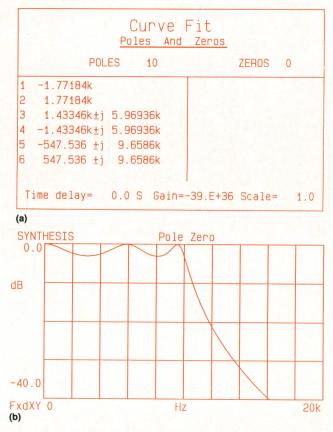

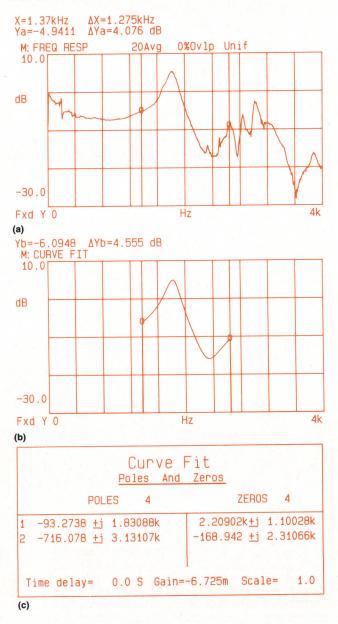

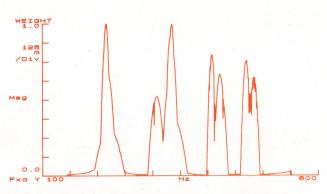

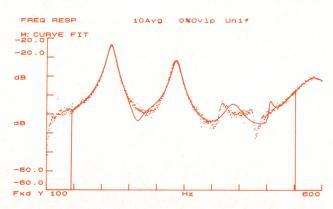

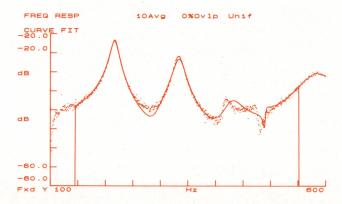

**Curve Fitter.** One of the most powerful analysis features in the HP 3562A is a multidegree-of-freedom, frequencydomain curve fitter for extracting the poles and zeros of a network from its measured frequency response function. The curve fitter can fit up to 40 poles and 40 zeros simultaneously for the entire response function or any portion defined by the display markers. In addition, the table of poles and zeros generated by the curve fit can be transferred to the synthesis table—a direct link between the instrument's modeling and analysis features. A curve-fit algorithm that can only fit clean data is of little practical use since most real-world measurements are contaminated by some amount of noise. The HP 3562A curve fitter removes biases caused by measurement noise, resulting in a greatly reduced noise sensitivity and, therefore, more accurate estimates of the pole and zero locations. See the article on page 33 for more details.

#### **Hardware Design**

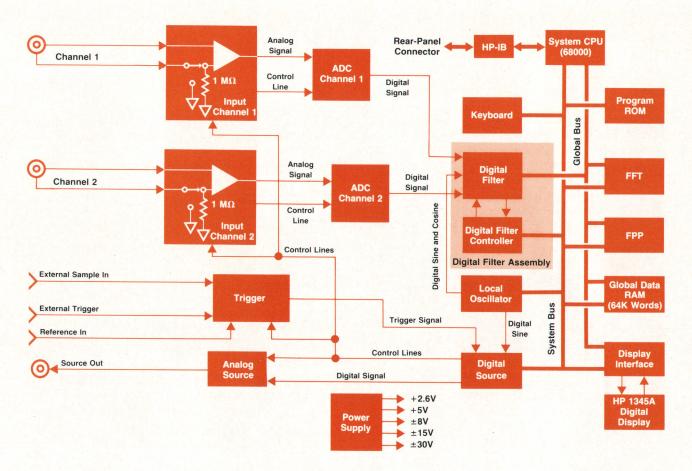

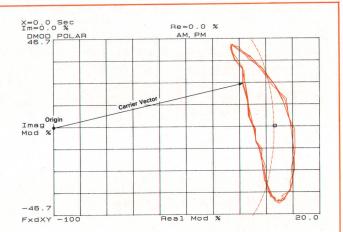

A block diagram of the HP 3562A's hardware system is shown in Fig. 2.

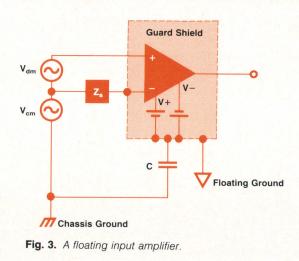

**Input Amplifiers.** Spectrum analysis for mechanical and servo applications requires that the analyzer's input amplifiers provide ground isolation (usually to reject dc and ac power-line frequency signals). Ground isolation at low frequencies can be achieved by running the input amplifiers on floating power supplies with the supply grounds driven by the shields of the input cables. This floating ground can then be used to drive a guard shield that encloses the floating amplifier's circuitry. This design is effective at rejecting dc common-mode signals and provides a large common-mode range, but is limited in its ability to reject higher-frequency common-mode signals.

Fig. 3 illustrates the problem. Common-mode signal  $V_{\rm cm}$  is dropped across the voltage divider formed by the source impedance  $Z_{\rm s}$  (which could be the resistance of the input cable) and the capacitance C between the floating ground and chassis ground. The voltage drop across  $Z_{\rm s}$  is then measured by the analyzer just as if it were any other differential-mode signal  $V_{\rm dm}$ . It can be seen that things get worse with increasing frequency. The fundamental problem here is that truly floating the amplifier is not practical since C cannot be made arbitrarily small in practice and the inputs are not balanced with respect to the chassis. In addition, since the source impedances to the two input terminals may not be quite the same, it is desirable to minimize the common-mode input currents by providing a high-impedance path for both signal inputs.

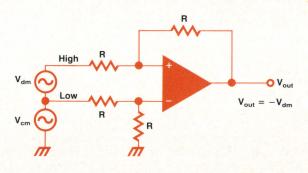

An effective way of providing high impedance for both inputs and good balance is to use a true differential amplifier (Fig. 4). For a perfect amplifier with a gain of -1and all resistors shown of equal value, the common-mode rejection (CMR) will be infinite (neglecting parasitic components). An added benefit is that common-mode rejection is achieved without requiring floating power supplies, which would be prohibitively expensive in a multichannel instrument. The input amplifiers in the HP 3562A are based on this true differential amplifier topology with circuitry to provide calibration of CMR and bootstrap circuits to increase common-mode range and reduce distortion.

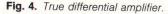

The two input paths in each of the HP 3562A's amplifiers contain programmable (0 dB, 20 dB, or 40 dB) attenuators, buffer amplifiers, and other circuits that contribute to imbalances in the two signal paths. To remove these imbalances (and improve CMR), a programmable circuit is used to adjust the gain of the low signal path. As shown in Fig.

## **Applications**

The HP 3562A covers a broad range of applications in control systems, mechanical systems, low-frequency electronics, and acoustics.

#### **Design of Closed-Loop Control Systems**

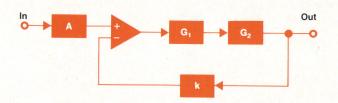

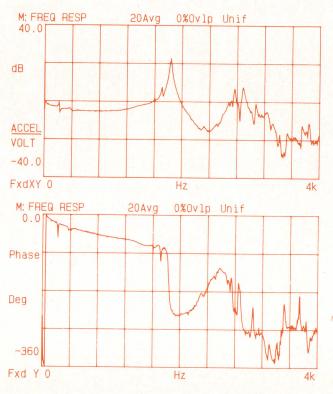

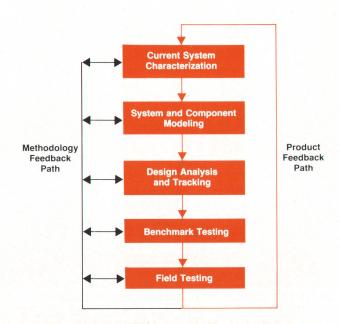

The general development process is shown in Fig. 1. A particular application of this development process is the design of closed-loop control systems. The design activity involves selecting components that, when connected in a specified topology, produce system performance consistent with the design specification. Closely related to this activity is the modeling activity developing equations to predict system performance. These equations are often transfer function relationships expressed as ratios of polynomials in the complex frequency domain.

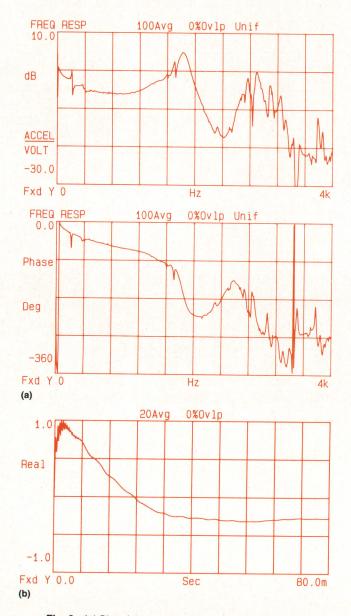

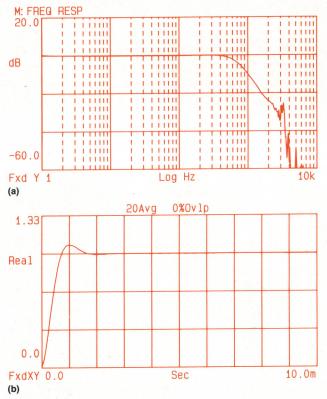

The design and modeling activities are simplified using the HP 3562A because of its built-in s-plane calculator and transfer function synthesis capability (see article on page 25). A designer can enter system information directly into the analyzer in polezero, pole-residue, or polynomial format. Conversion between these formats is possible. Once the system information is entered, the analyzer will compute and display the frequency response of the system. The result can be displayed in gain/phase form, as a Nyquist diagram, or as a Nichols chart. The designer can then easily perform other calculations on the synthesized waveform. For example, the inverse transform of the frequency response can be displayed with one keystroke to identify the impulse response of the system. By pressing another key, this waveform can then be integrated to simulate the step response.

The test activity involves making measurements to determine actual system performance. Designers requiring both FFT and swept sine measurements can use the HP 3562A to perform both functions. The HP 3562A provides not only frequency domain test capabilities, but also time domain test functions. Its waveform recording features allow the control system designer to measure time domain functions such as impulse, step, and ramp responses.

The analysis activity studies measured performance. In cases where desired performance, such as gain-phase margin, overshoot, or undershoot has been estimated, analysis consists of comparing measured results against the expectation. This comparison can be as simple as reading marker values or using the

5, this is accomplished by increasing the gain through the low path by raising the value of  $R_d$  and then driving the grounded end with a signal that is  $-K \times B$ , where K is the gain of a multiplying digital-to-analog converter (DAC). Increasing the DAC gain reduces low-path gain to the point, where CMR is maximized.

An algorithm for optimum adjustment of the DAC was developed that requires only two data points to set the gain HP 3562A's front and back display format.

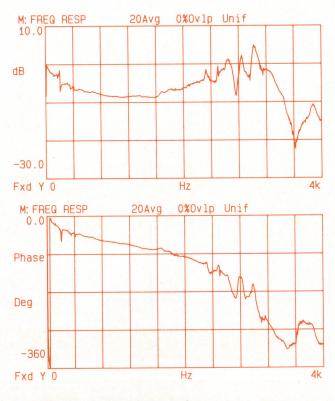

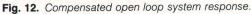

Often designers are constrained to measure control systems under operating conditions with the loop closed. Although the closed-loop response is measured, the open-loop response is desired. The HP 3562A provides an analysis function that can compute the open-loop response directly from closed-loop data with just one keystroke.

An extremely powerful analysis tool for the control system designer is the HP 3562A's curve fitter (see article on page 33), which extracts system poles and zeros from measured frequency response data for comparison against expected values. Furthermore, the curve fitter provides the link between the analysis and model activities in the development process, because of its ability to pass curve-fit data to the transfer function synthesis function.

#### **Vibration Analysis**

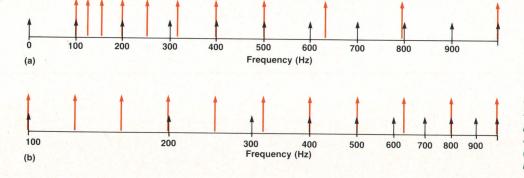

Vibration measurements on rotating machinery are extremely important. In many cases, the vibration signals of interest are modulation signals on a carrier frequency which corresponds to the shaft rotation speed. As an example, a broken tooth on a rotating gear can result in amplitude-modulated vibration signals. In a belt-driven pulley system, the dynamic stretching of the belt can produce frequency-modulated or phase-modulated signals.

The HP 3562A can perform AM, FM, or PM demodulation on these vibration signals even if the carrier frequency (shaft speed) is unknown.

#### **Electronic Filter Design**

All of the major modeling, test, and analysis features can come into play in solving filter design problems (see article on page 25 for examples). The initial filter model (i.e., transfer function) can be entered into the synthesis table in the form most familiar to the designer and then the model's frequency response function can be synthesized. Log resolution measurements or log-sine sweeps are appropriate for measuring broadband filter networks. High-Q notch filters can be accurately characterized using zoomed linear-resolution measurements or narrow sine sweeps. By applying the HP 3562A's curve fitter to these linear or log frequency measurements, the poles and zeros of the actual filter can be extracted for comparison with the model.

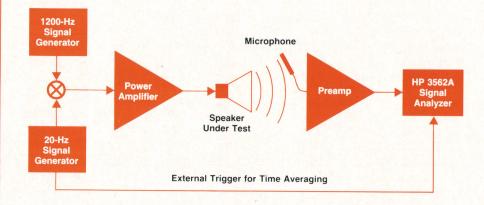

#### **Audio and Acoustics**

Noise identification and control are becoming more important in many environments. With its two input channels, the HP 3562A can make acoustic intensity measurements to determine sound intensity and direction. In the audio field, the instrument's digital demodulation capability has proven to be very effective in analyzing modulation distortion in phonograph pickup cartridges and loudspeaker systems.

#### **Bibliography**

1. Control System Development Using Dynamic Signal Analyzers, Hewlett-Packard Application Note 243-2.

correctly. A common-mode signal is internally connected to both differential inputs and the DAC is set to each of its extreme values. The relationship between the two resulting measured signal levels is then used to interpolate to obtain the optimum DAC gain setting. The resulting CMR is better than -80 dB up to 66 Hz and -65 dB up to 500 Hz.

One-megohm-input buffer amplifiers are inserted between the inputs and the differential amplifier stage to

Fig. 2. Hardware block diagram of the HP 3562A.

provide impedance conversion. The common-mode range of these amplifiers is increased and distortion is reduced by adding bootstrap amplifiers that drive the buffer amplifier power supplies (Fig. 5). These bootstrap amplifiers are unity-gain stages with  $\pm$  dc offsets added to the outputs so that the buffer amplifier supplies follow the ac input voltage. Thus, the input buffer amplifiers only need to provide correction to the signals present within their supply rails. In addition, the op amps used in these amplifiers are therefore able to work over a common-mode

range that would otherwise be beyond their maximum supply rail specification. The resulting common-mode range for the HP 3562A is  $\pm$ 18V on the most-sensitive range (-51 dBV) and distortion is suppressed more than 80 dB below full scale.

**Digital Circuitry.** For certain analyzer frequency spans, the data collection time (time record length) will be shorter than the data processing time. As a result, part of the input data will be missed while the previous time record is being processed. In this case, the measurement is said to be not real-time. As the frequency span is decreased, the time record length is increased, and a span is reached where the corresponding data collection time equals the data processing time. This frequency span is called the real-time bandwidth. It is at this span that time data is contiguous

**Fig. 5.** Input amplifier configuration used in the HP 3562A.

and all input data is processed. Decreasing the span further results in data collection times longer than the data processing time. These measurements are said to be real-time.

Designing for a real-time bandwidth of 10 kHz (single channel) requires data processing times of less than 80 ms. It was apparent that a single processor could not perform the many computational tasks (fast Fourier transforms and floating-point calculations in particular) that are required within this amount of time. Consequently, the choice was made to develop separate hardware processors for these computational needs. The large real-time bandwidth of the HP 3562A is possible because of the use of multiple hardware processors and a dual-bus digital architecture (see right half of Fig. 2).

Before pipelined parallel data processing can begin, the input signals must be digitized and filtered to the current frequency span. Signals enter the analyzer and are conditioned by the programmable-gain, differential-input amplifiers described above. Low-pass anti-aliasing filters with a cutoff frequency of 100 kHz attenuate unwanted frequency components in the conditioned signal. The signal is then converted to digital data by analog-to-digital converters (ADCs) using the same design that was used in the earlier HP 3561A.<sup>1</sup> The data is then filtered to appropriate frequency spans by custom digital filters. Separate digital filters exist for each input channel.

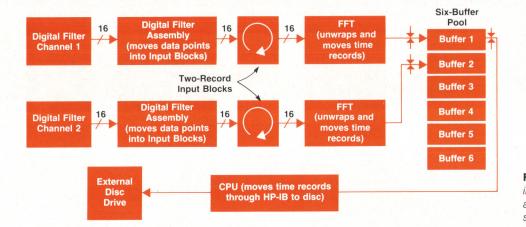

The digital filters provide the gateways for data into the digital processing portion (Fig. 2). The architecture includes a system central processing unit (CPU), an FFT processor, a floating-point processor (FPP), a shared memory resource (global data RAM), an interface to the display, and two separate digital buses that allow simultaneous communication and data transfer.

The CPU controls a data processing pipeline by issuing commands, reading status, and servicing interrupts for the digital filter controller, FFT processor, FPP, and display interface. The CPU also services the digital source and front-end interface, local oscillator, keyboard, and HP-IB. The CPU design consists of an 8-MHz MC68000 microprocessor, a 16K×16-bit ROM, a 32K×16-bit RAM of which 8K×16 bits is nonvolatile, a timer, HP-IB control, power-up/down circuitry, and bus interfaces. The CPU communicates with each of the hardware processors as memory mapped I/O devices over the system bus, which is implemented as a subset of the 68000 bus.

The other bus in the architecture, the global bus, provides a path to the global data RAM. This memory is used by all of the hardware processors for data storage. After the data has been digitized and filtered to the current frequency span, the digital filter stores it into the global data RAM. The CPU is signaled over the system bus when a block of data has been transferred, and as a consequence, the CPU instructs the FFT processor to perform a time-to-frequency transformation of the data. The FFT processor accesses the global data RAM, transforms the data, stores the result back into memory, and then signals the CPU. The CPU now commands the FPP to perform appropriate floating-point computations. The FPP fetches operands from the global data RAM, does the required calculations, and then stores the results back into memory. When finished, the FPP signals the CPU. The CPU then reads the data, and performs coordinate transforms on it as well as format conversions in preparation for display. The data is again stored into the global data RAM. The CPU finally instructs the display interface to transfer the data to the display. (The display used is the HP 1345A Digital Display, which requires digital commands and data to produce vector images.)

The above description describes one data block as it is transferred from digital filter to display. However, the HP 3562A Analyzer does not process one block of data at a time, it processes four. That is, while display conversions of block N-3 are being done by the CPU, block N-2 is being operated on by the FPP, block N-1 is being transformed by the FFT processor, and block N is being filtered by the digital filter. Simultaneous operation of all processors provides the computational speed necessary to produce a large real-time bandwidth of 10 kHz.

As a consequence of the data processing architecture, the global memory system had two major requirements. The first was that multiple processors needed access to the memory. This required an arbiter, a decision maker, to monitor memory requests and allocate memory accesses (grants) based on a linear priority schedule. Devices are serviced according to their relative importance, independently of how long they have been requesting service. Each requesting device has associated with it a memory request signal and a memory grant signal. When a device needs access to the memory, it asserts its memory request. The global data RAM prioritizes all requests and issues a memory grant to the highest-priority device. That device is then allocated one bus cycle.

The second major requirement placed on the global memory system was minimal memory cycle time to satisfy instrument real-time bandwidth needs. Computer simulations were done to model the effects of memory cycle time on real-time bandwidth. It was concluded that cycle times less than 500 ns would satisfy the instrument's real-time bandwidth requirements.

To optimize memory cycle time, the timing for the global memory system is constructed from a digital delay-line oscillator. Three digital delay lines are connected in series, with the output of the third delay line. Individual timing signals were customized for the  $64K \times 16$ -bit dynamic RAMs and arbiter using combinational logic operating on signals from 10-ns delay taps on the delay line oscillator. As implemented, global memory cycles are available every 470 ns.

The FFT processor can perform both forward and inverse fast Fourier transforms and windowing. It is designed around a TMS320 microprocessor. Although an on-board ROM allows the TMS320 to execute independently, the FFT processor is slaved to the CPU. Commands are written to the FFT processor over the system bus, and the FFT processor accesses the global data RAM for the data to be transformed and any user-defined window information. Operations are executed, and the CPU is interrupted upon completion. The FFT processor computes a 1024-point, radix-4 complex FFT in 45 ms.

The FPP is constructed from six AM2903 bit-slice microprocessors using conventional bit-slice design techniques. It can operate on three different data formats: two's complement integer (16 bit), single-precision floating-point (32 bit), or double-precision floating-point (64 bit). Besides addition, subtraction, multiplication, and division, the FPP can perform 81 customized operations. A list of FPP instructions, called a command stack, is stored in the global data RAM by the CPU. The list consists of a 32-bit command word (add, subtract, et cetera), the number of entries in the data block to be operated on, constants to indicate if the data block is real or complex, the beginning address of the data block in the global data RAM, and the destination address for the results. The FPP is then addressed by the CPU and the starting address of the command stack is given. The FPP executes the command stack and interrupts the CPU upon completion.

The digital filter assembly consists of two printed circuit cards. One card, the digital filter board, contains two sets (one per input channel) of custom integrated circuits designed for digital filtering. These integrated circuits were leveraged from the design of the HP 3561A.<sup>2</sup> The other card, the digital filter controller board, supplies local information to the digital filter board and contains the interface to the system bus. Digitized data is supplied to the digital filter from the ADCs at a 10.24-MHz rate. Upon command from the CPU, the digital filter can operate on the data in different ways. It can pass the data directly to the global data RAM (as is required if the user wants to view time data). It can frequency translate the data by mixing it with the digital equivalent of the user-specified center frequency, filter unwanted image frequencies (required in a zoom operation which enables the full resolution of the analyzer to be concentrated in a less than full span measurement), and store to the global data RAM. Or it can filter the data without any frequency translation and store to the global data RAM (required in the baseband mode where the start frequency is 0 Hz and the span is less than full span). The data can be operated on simultaneously in different modes, thus providing the analyzer the ability to view input data simultaneously with frequency data. The design is the most complex digital assembly in the HP 3562A, and is implemented using a number of programmable logic devices, direct memory access (DMA) controllers, and large-scale-integration counters.

**Throughput.** Throughput means acquiring input data, filtering it, processing trigger delays, and writing the data to the disc as fast as possible. To accomplish this, the HP 3562A has built-in disc drivers for HP Command Set 80 (CS/80) disc drives (e.g., HP 7945 and HP 7914), HP Subset 80 (SS/80) disc drives (e.g., HP 9122 and HP 9133D), and other HP disc drives such as the HP 9121, HP 9133XV, HP 82901, and HP 9895. These disc drives can be used for general save and recall functions in addition to throughput. The drives most suited for throughput are the CS/80 or SS/80 hard disc drives. The software disc drivers are tuned for these drives.

The throughput is accomplished with three internal processors to pipeline the transfer process (see Fig. 6). The digital filter assembly digitally filters the data for a channel into a rotating buffer with enough room for two time records. This allows one time record to be accumulated while the other record is moved out of the buffer. When the instrument is acquiring data in triggered mode, the digital filter assembly is putting the data in the rotating buffer even before the trigger is received. The data before the trigger is needed if a pretrigger delay is specified. Since the start of data (trigger point if no trigger delay) can occur anywhere in the rotating block, the full time record will not be contiguous in memory if the start of data is more than halfway into the buffer. The first part of the data will be at the end of the buffer and the last part of the data will be at the beginning of the buffer (i.e., the data is wrapped).

The next step is for the FFT processor to move and unwrap the data into another buffer. This buffer is one of a

**Fig. 6.** Throughput data flow during a data acquisition to disc storage. (All processors are running simultaneously.)

set of six rotating buffers. The FFT processor is fast enough to move an entire time record out of the input block before the digital filter assembly overwrites it, except for a 100kHz frequency span, which is faster than real-time anyway. The CPU moves the contiguous data in time record blocks through the HP-IB to the disc drive. To cut down on the disc overhead, the entire throughput operation is set up as a single disc write command. The six buffers help to smooth the nonlinear transfer rate to the disc.

The limit on the transfer rate is usually the CPU handshaking data out of the HP-IB chip. The CPU executes a tight assembly language loop to transfer data (about 60 kbytes/s). Most hard discs can receive data faster than this. This transfer rate translates into a 10-kHz real-time frequency span for a one-channel measurement.

Since throughput is essentially a real-time operation, the digital filter channels must never stop transferring data to memory, or gaps will appear in the data. If both channels are being throughput to the disc, then the data is interleaved on the disc in time record increments (Channel 1 followed by Channel 2). If both channels are being throughput in triggered mode, then both channels are triggered at the same time regardless of trigger delay. This allows both channels to be synchronized on time record boundaries. If the user specifies a cross-channel delay of greater than one time record, then an integral number of time records are thrown away from the delayed channel rather than wasting space on the disc with unused data. Hence, with the same number of records throughput to the disc in this mode, there will be a sequence of the undelayed channel records, followed by zero or more interleaved records (Channel 1 followed by Channel 2), followed by the remainder of the delayed channel records.

Since the throughput is normally done with one write command to the disc, the disc will fill an entire cylinder before moving the disc heads to the next cylinder (head step). Each cylinder consists of multiple heads, each on a separate surface (i.e., a track). The time to step the head one track is not long. If the track has been spared (i.e., because of a bad spot on the disc), the disc head automatically steps to the replacement logical track, which could be halfway (or more) across the disc. This could adversely affect the real-time data rate. To avoid this problem, the instrument does not use any logical track that has been spared (replaced) for throughput. There will be a gap in the logical address space on the disc, but skipping the spared track only requires two head seek times. The spared track table can only be read from a CS/80 disc drive. If a spared track is in the throughput file used, then one disc write transfers data before the spared track, and another write is used for data after the spared track. The HP 3562A can skip up to nine spared tracks in each throughput file (identified in the throughput header) in this manner.

Any throughput data in the file can be viewed by the user as a time record or used as a source of data for a measurement. When performing a measurement of the throughput data, the data is input back into the digital filters for possible refiltering. This allows data throughput at the maximum real-time span (10 kHz, one channel) when test time is valuable, and then performing the measurement later at a desired lower span (e.g., 2 kHz). Since throughput data is processed off-line, more flexibility is allowed on this data than may be possible with a normal on-line measurement. Data from anywhere in the throughput file can be selected for postprocessing (i.e., a selected measurement) by specifying a delay offset when measuring the throughput. For a measurement on a real-time throughput file, the user can specify the exact amount of overlap processing to be used during averaging. Increased flexibility is realized by being able to continue a measurement from anywhere in the throughput file, which allows a measurement on the throughput data in a different order than it was acquired.

#### **Operating System**

The operating system used by the HP 3562A can be described as a multitasking system with cooperating processes. The operating system provides task switching, process creation, process management, resource protection (allocation), and process communication.

The operating system manages the use of processes. A process is a block of code that can be executed. In a multitasking system, several processes can be executed simultaneously. Since there is no time slicing (using a timer interrupt to split CPU time between processes), cooperation between processes is essential. To share CPU resources between processes, explicit suspends back to the operating system must be performed about every 100 ms. Since our development language (Pascal) is stack oriented, there could be a problem with multiple processes. Does a process share a stack with another process? How do they share it? Because of demands on the CPU RAM (i.e., local data, states, et cetera), the stack RAM space was in short supply, so we chose to implement a hybrid stack management system.

We started implementing a system with only one stack instead of a stack for each process. This was accomplished by making one restriction upon the software designers. Breaks to the operating system (suspends and waits) could only be made in the main procedure in a process, which was not unreasonable for our original code expectations. Our Pascal development language allocates the procedure variables on top of the stack upon procedure entry and afterward references these variables with a base address register. The stack pointer is not used to reference the variables. The top of stack can be moved without affecting the access of the variables in the main procedure. This allows each process to have its own stack for its main procedure that is exactly the right size, and also a (possibly separate) stack for procedure calling. When a process ends, a call back to the operating system records the stack segment for the main procedure as being empty so that it can be reused.

This method of stack allocation presented problems when the code size grew significantly (to 1.1 Mbytes), but the RAM grew only slightly (to 64K bytes). Some processes became larger and the restriction on waits became unwieldy. Therefore, a second method was implemented of allocating entirely separate stacks (partitions) for some processes (e.g., calibration and HP-IB control). There was not enough RAM to do the same for all processes, so a hybrid system was maintained. A partition concept was defined to allow a single process to use a partition (allocated at power-up) or one of a group of processes to use a partition at any one time (e.g., one of the HP-IB processes). The addition of partitions allowed us to gain the maximum utility out of the limited RAM available.

The operating system is semaphore based. The classic Dijkstra p() and v() operations<sup>3</sup> are used for resource protection and process communication. These operations have been implemented as counting semaphores with the only allowable operations of wait (corresponds to p()) and signal (i.e., v()). A counting semaphore can be defined as a positive integer (may never become negative).

A signal is defined as an increment operation. A wait is defined as a decrement operation where the result may not be negative. If the decrement would cause the result to be negative, then the process execution is blocked until the semaphore is incremented (i.e., a signal is sent by some other process), so that the decrement can be successful.

The actual implementation of a semaphore is different. The integer does become negative on a wait and the process is blocked in a queue of waiting processes associated with each semaphore (semaphore wait queue). A signal where the previous value before the increment was negative will unblock the first process in the wait queue (i.e., it can run again). In this sense, a semaphore count, if negative, represents the number of processes waiting on the semaphore.

There are generally two types of semaphore use: resource protection and process communication. A resource protec-

tion semaphore is initialized with a value that is the number of resources available (generally one). An example of this in the HP 3562A is the floating-point processor; only one process can use it at a time. A process uses a resource semaphore by executing a wait before the block of code that uses the resource, and a signal after that block of code. All processes that use this resource must do the same thing. The first process executing the wait decrements the semaphore from 1 to 0 before using the resource and afterward increments (signals) the semaphore back to 1. If a second process tries to wait on the resource after the first process has acquired the resource (wait), then the second process will be blocked (it cannot decrement 0 to -1) until the first process has signaled (released) the resource. A semaphore is also used to protect critical sections of code from being executed by two processes simultaneously.

A process communication semaphore (initialized to 0) is used by two processes that have a producer/consumer relationship. The producer signals the semaphore and the consumer waits on the semaphore. An example of a consumer in the HP 3562A is the marker process, which waits for a marker change before moving the marker on screen, while the producer is the keyboard interrupt routine, which detects that a marker change is requested and signals the marker process.

In many cases, a process communication semaphore is not enough. The consumer must know more about what is to be done. Therefore, a communication queue which has one entry for each signal by the producer is associated with the semaphore. This combination is known as a message queue. An example is the keyboard interrupt routine (producer) and the front-panel process (consumer). A queue containing key codes is associated with the semaphore.

Queues, a first-in-first-out construct, are also supplied by the operating system. As mentioned above, queues are mainly used to communicate between processes, but are also used by the operating system (i.e., the process ready queue) and other processes to keep a list of information. Another variant of the queue definition is the priority queue, where an addition-to-a-queue operation inserts new entries in order by a priority key. The operating system process ready queue is an example of a priority queue in the HP 3562A. The priority is set by the scheduling process to determine the relative execution order of several processes.

Command input to the HP 3562A is from three processes representing the keyboard, autosequence, and HP-IB. Each process accepts codes from the appropriate source, converts them to a common command function format, and invokes the command translator. The command translator controls the main user interface, the softkey menus, command echo field, numeric entry, and translation of the command function into a subroutine call to do the requested operation. The command translator is table driven. A single data base of all keys is maintained with all related softkey menus and actions to be performed when a key is pressed. A single command translator presents a consistent interface to the user, regardless of the source of the commands.

The following is an example of the power of a multitasking operating system. It shows how four processes can be run at the same time within the HP 3562A. There is a measurement running on one trace, a view input on another trace, the display process itself, and a plot process. To see the results, press:

| PRESETRESET                      | (put HP 3562A in known            |  |

|----------------------------------|-----------------------------------|--|

|                                  | state and start measurement)      |  |

| UPPERLOWER                       | (display both traces)             |  |

| <b>B VIEW INPUT</b> INPUT TIME 1 | (start view input in other trace) |  |

| PLOT START PLOT                  | (start plot process)              |  |

|                                  |                                   |  |

The plotting is performed in parallel with the measurement and view input. This is called "plot on the fly." Resource semaphores are used to protect hardware from simultaneous use by several processes. Communication semaphores are used to communicate display status to data taking processes. Buffer lock flags are used to protect the display buffers from use by both the display and the plot.

In summary, the use and implementation of the operating system in the HP 3562A show the trade-offs that occurred during project development. The operating system has enough power and flexibility to implement otherwise very difficult operations (e.g., plotting during a measurement), but is simple enough not to impose much overhead. Less than 2% of the processor time is spent in the operating system.

#### Autosequence

An autosequence is a programmable sequence of key presses that can be invoked by a single key, which makes repetitive operations easier for the user. It is the simple programming language built into the HP 3562A. In the learning mode (edit autosequence), all completely entered command lines, from hard key to terminating key, are remembered in the autosequence. The line-oriented editor allows line deletion, addition, and replacement. A looping primitive and a goto command allow repetitive commands. Other autosequences can be called as subroutines. The autosequence can be labeled with two lines of text, which will replace the key label that invokes the autosequence.

Up to five autosequences in the instrument can be stored in battery-backed CMOS RAM. Since CMOS RAM is limited, an implementation was chosen that takes minimal memory to store an autosequence. The storage mechanism saves either the keycode (0 through 69) for the key pressed (only takes one byte) instead of the HP-IB mnemonic (4 bytes), or a unique key function token (over 900 functions defined by 2 bytes). This allows storage for an autosequence of 20 lines with an average of 10 keys/line. The command strings seen in the autosequence edit mode are only stored in a temporary edit buffer (not stored in CMOS RAM). When the edit mode is engaged again, the stored keys are processed through the command translator without executing the associated actions to rebuild the command strings. The commands are shown on the screen as they are being rebuilt.

The softkey menus of the HP 3562A may vary when the measurement mode changes. For example, in swept sine mode, there is a softkey STOP FREQ under the **FREQ** key. In linear resolution mode, the ZERO START softkey is in the same location (softkey 4). Key codes (e.g., softkey 4) are stored in the autosequence. If an autosequence that has this key sequence in it is run in both modes, a different

action could take place (zero start versus stop frequency). This is not what the user expects. To solve this problem, any time a variant softkey menu is displayed because of a key press, the variant menu number is stored in the autosequence following the key. When the autosequence is edited, the variant menu is forcibly displayed so that the user always sees the same command echo regardless of the measurement mode. When the autosequence is executed, the actual key function (e.g., stop frequency) is obtained by looking up the softkey number in the current softkey menu. If the key function is found, the new keycode is executed instead of the old keycode. This allows softkey functions to move in the menu in different modes. If the key function is not found, an error results and the autosequence stops. The additional overhead for this function is one byte for each variant menu displayed in the autosequence. Although the storage overhead is not very significant, the software to execute the autosequence became more complex.

While executing the autosequence, the front-panel keys are locked out (except **AUTO SEQ** PAUSE ASEQ). This is necessary because there is only one base translator with three command sources (keyboard, autosequence, and HP-IB), and only one current menu can be remembered at a time.

| MNEMONIC T                                                                      | ABLE           | HELP TE>                                                                                                                           | TAREA                                                                                                                |

|---------------------------------------------------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| "FREQ"<br>freq help<br>"AVG"<br>avg help<br>"WNDO"<br>window help               |                | tokense                                                                                                                            | ion of help with embedded<br>encoded as below in<br>CTER VALUE                                                       |

| CHARACTER                                                                       | (Bit in byte 1 | ) (Bit in byte 2<br>0 7 6 5 4 3 2 1 0                                                                                              |                                                                                                                      |

| ASCII char<br>byte token<br>word token<br>text macro<br>break line<br>paragraph | 1001 —         | word token           word token           word token           word token           text token           1           1           1 | see BYTE TOKEN TABLE<br>see WORD TOKEN TABLE<br>and WORD INDEX TABLE<br>(except 4094, 4095)<br>see TEXT TOKEN TABLE  |

| BYTE TOKEN<br>(64 entrie                                                        |                | ORD INDEX TABLE<br>(25 entries)                                                                                                    | E WORD TOKEN TABLE<br>(1548 entries)                                                                                 |

| "," entry 0<br>"." entry 1<br>"1" entry 2<br>"2" entry 3<br>"Channel" 4         | ot             | ffset to entry 0<br>ffset to entry 64<br>ffset to entry 128                                                                        | <ul> <li>"ACPT" entry 0</li> <li>"Hertz" entry 1</li> <li>"Not" entry 2</li> <li>"Push" entry 3</li> <li></li> </ul> |

| TEXT TOKEN<br>(N entries)<br>point to 1 st to<br>point to 2 nd 1                | ext            |                                                                                                                                    |                                                                                                                      |

**Fig. 7.** Help table structure (top), definitions of two-byte character values (middle), and examples of token table entries (bottom).

For instance, from the keyboard, the user presses **WINDOW** UNIFRM (softkey 3), and from autosequence, **SELECT MEAS** FREQ RESP (softkey 1). If the key presses were interleaved between the two command sources when the functions are processed, then the commands would appear to be **WINDOW SELECT MEAS** AUTO CORRelation (softkey 3). The wrong functionality would be invoked in this case. To prevent this situation, these two processes are synchronized and the autosequence lets the HP-IB commands execute only between autosequence lines. Each autosequence line always starts with a hard key (i.e., it has no memory of a previous softkey menu).

Autosequence commands may spawn child processes to do specific actions (e.g., a measurement). The front panel will continue to accept a new command before the child process is finished, but the autosequence will wait until the child process is finished before executing the next line. The required synchronization is provided by the operating system, which keeps track of the status of the children of the command front ends and communicates the information through a semaphore to the command source (e.g., autosequence).

#### **Help Text Compression**

The HP 3562A has a help feature for 652 soft and hard keys in the instrument. Help information is derived from the HP-IB mnemonic for the key pressed. The help display consists of information derived from the key table (full command name, type of key, number and type of parameters) and a text description of the key. The text description can take the entire display area (48 columns by 20 lines). If the average text description per key is five lines, then just the text portion of the help feature would consume 156,000 bytes. The actual help text for the HP 3562A takes 157,125 characters (bytes).

To save ROM space, the text is compressed before putting it in ROM (see Fig. 7). The method used is a token replacement of duplicate words used in the text. The two-pass compression program reads the input text on the first pass, breaks it into words, and updates an occurrence count for each unique word (29,509 unique words). At the end of the first pass, the words are sorted by their occurrence frequency. Token tables are created for multiple-use words to be replaced in the text during the second pass.

The ASCII character set (unexpanded) is a seven-bit code. To encode the tokens in the output text, the high-order bit (bit 7) is set in the byte. This allows 128 tokens to be encoded in a byte, which is not enough. A word token allows more tokens (32,767), but takes twice the memory to represent the output text. To compromise, both byte tokens and word tokens are used. The 64 most-used words are encoded into a byte token (bit 6 set) and 32,767 other text functions can be encoded into a word token.

The word text functions are split into two groups: word tokens and special functions. Special functions have bits 4 and 5 set, allowing 4095 functions to be encoded and leaving 12,288 possible word tokens (1548 actually used). The special functions are split into two groups: special formatting commands and text macros. The text expander in the HP 3562A also formats the displayed text. The text in the help table is in free format, just words separated by spaces and punctuation. The expander knows how to leftjustify text on the screen and break lines on word boundaries. In addition, it knows two special formatting commands: break line (go to next line) and start paragraph. The last of the special functions that are encoded are text macros. Groups of words can be defined and included in multiple places (useful to describe numbers). There is space for up to 4094 text macros. The 64 most-used byte tokens save almost as much space as the 1548 word tokens (45,189 bytes versus 55,363 bytes).

To save as much ROM space as possible in the help table, several concessions to size, space, and speed were made. To make the pointers to text shorter, 16-bit unsigned offsets are used instead of 32-bit pointers in the help mnemonic table (converts HP-IB mnemonics to text addresses), the text macro table, and the word token index table. Later, the help mnemonic table had to be changed to 32-bit pointers because the size of the tables and the help text had exceeded 64K bytes (the limit of a 16-bit offset). Since words vary in size, the byte and word token tables are organized as a linked list. Hence, they must be traversed to access any given token. This is acceptable for the 64 byte tokens, but takes too long for the 1548 word tokens. Therefore, a word token index table was created to index into every 64 word tokens, keeping the worst-case lookup sequence to 64 entries.

Compressing text to save room can be a good investment. In the HP 3562A, the text is compressed down to 36% of its original size through word replacement, saving 100,000 bytes of ROM.

Compression may be a good idea, but how long does it take to compress and decompress the text? The compression into assembler code takes approximately six hours on an HP 1000 Computer. However, the decompression of a worst-case full page takes less than a second, so it is acceptable for a help display.

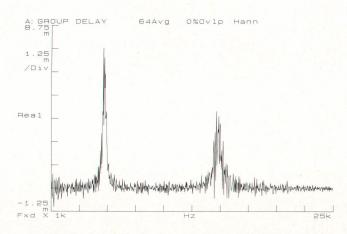

Fig. 8. Automath plot for group delay calculation.

#### Automath

The HP 3562A includes a rich set of math operations available to the user to postprocess the measurement data. In addition, automath adds the ability to perform calculations on the fly during a measurement for custom measurement displays (e.g., group delay). Automath also adds the ability to title a custom measurement display on the trace.

In many cases the automath calculation does not slow down the measurement appreciably. This is because most math operations (except log and FFT-type operations) are performed by the floating-point processor (FPP) in parallel with most operations in a measurement.

Automath is in reality an autosequence that is limited to math, measurement display, and active trace keys. When the MEAS DISP AUTO MATH keys are pressed, the automath autosequence is run to produce a sequence of math operations and the initial measurement displays are set. The measurement converts the sequence of math operations into a stack of FPP commands and appends it to its own FPP stack. This stack is retained for use on every measurement average; the stack is only rebuilt if something changes (e.g., a reference waveform is recalled). Considerable time is saved in this optimal case. For operations that the FPP does not execute directly, there is a pseudo FPP command that causes the FPP to stop and interrupt the CPU, which interprets and executes the command and then restarts the FPP upon completion. Since the math commands are generated once, a copy of the changed state of the data header must be saved during generation to be restored on every data average while the FPP computes the automath.

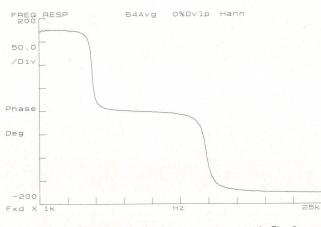

Fig. 8 shows the resultant traces generated by automath for group delay where group delay =  $-\Delta$ phase/ $\Delta$ frequency. Math is applied to the complex data block, not the coordinates that are displayed (e.g., magnitude and phase), so the phase of the frequency response must be expressed in complex form. The natural log of the complex data will put the phase information in the imaginary part of the data. Multiplying by 0 + j1 results in negative phase being in the real part of the data. The real-part command clears the imaginary part of the data, resulting in negative-phase information only. The differentiate command completes the group delay by differentiating with respect to frequency. Fig. 9 shows the phase of the frequency response measurement used by automath for the plot in Fig. 8.

#### Autocalibration

The HP 3562A calibration software has two parts. First, a calibration measurement routine calculates complexvalued correction data for the two input channels. These calibrations can run automatically to account for temperature-induced drift in the input circuits, including the power-up temperature transient. Second, correction curves (one for each display trace) are generated on demand for use by the measurement software. These correction curves combine the input channel correction data with analytic response curves for the digital filters to provide complete calibration of the displayed measurement results.

The HP 3562A input channels have four programmable attenuators.<sup>1</sup> The first, or primary, attenuator pads (0 dB, -20 dB, and -40 dB) each have significantly different frequency response characteristics. As a result, separate calibration data is required for each primary pad. Since the HP 3562A measurement software can perform both single-channel and cross-channel measurements, it may demand any of 15 distinct correction curve formats (see Fig. 10). Rather than collect 15 sets of data during calibration, six sets are carefully chosen so that the remaining nine sets can be derived.

The first choice for these basic six sets would be the single-channel calibrations A<sub>00</sub>, A<sub>20</sub>, A<sub>40</sub>, B<sub>00</sub>, B<sub>20</sub>, and B<sub>40</sub> (the subscripts refer to a particular pad of the primary attenuator). The HP 3562A single-channel calibration hardware and techniques are adapted from the HP 3561A.<sup>4</sup> Two classes of errors can be identified in this technique. One class of errors has identical effects in both channels, and therefore has no effect on the accuracy of a cross-channel correction derived from single-channel corrections. Finiteresolution trigger phase correction is an example of such an error term. The other class of errors has different effects in each channel, and therefore will degrade the accuracy of derived cross-channel corrections. Slew-rate limiting of the pseudorandom noise calibration signal by the input channel amplifiers is an error of the second class. While the cumulative errors in this second class are small with respect to the single-channel phase specification (±12 degrees at 100 kHz), they are too large to provide state-of-theart channel-to-channel match performance.

Therefore, the basic six calibration data sets must allow cross-channel corrections to be derived with no contribution from single-channel terms. The highlighted elements of Fig. 10 identify the basic six sets. A typical relationship between derived and basic cross-channel corrections is:

$$B_{40}/A_{00} = [B_{40}/A_{20}][B_{00}/A_{00}]/[B_{00}/A_{20}]$$

where the square brackets enclose stored terms.

Single-channel correction data is derived from singlechannel and cross-channel terms. For example:

$B_{40} = [A_{00}](B_{40}/A_{00})$

where  $B_{40}/A_{00}$  is derived as shown above.

The five basic cross-channel corrections are, like the single-channel correction, measured during the calibration routine. The periodic chirp source is connected internally to both channels for a bare-wire frequency response measurement, a direct measure of input channel match. The periodic chirp provides even distribution of energy over the whole frequency span of interest. It is also synchronized with the sample block duration to eliminate leakage effects.

Now consider the corrections for the second, third, and fourth input attenuators (secondary pads). The primary pad correction data already contains corrections for the particular secondary pads engaged during primary pad calibration. Thus, secondary pad correction must account for changes in the input channel frequency response when different secondary pads are engaged. These relative secondary pad corrections are negligible when compared with the singlechannel specification. However, their effects are significant for channel-to-channel match performance.

A pair of bare-wire channel-to-channel match measurements is used to generate relative calibration data for the secondary pads. One channel-to-channel match measurement is used as a reference-the absolute correction for its secondary pad configuration is contained within the primary pad data. In the other channel-to-channel match measurement, one secondary pad is switched in one channel. The ratio of these two channel-to-channel match measurements is the relative correction for the switched pad with respect to the reference pad. For example, consider a reference configuration of 0-dB primary pad (subscript 00) and 0-dB, 0-dB, 0-dB secondary pads (subscript 0,0,0) in both channels. Increment the last attenuator in Channel 2 to 2 dB for a configuration of 00-0,0,2. Then the relative correction for the -2-dB pad in the last attenuator of Channel 2 is calculated from:

### $(B_{00-0,0,2}/A_{00-0,0,0})/(B_{00-0,0,0}/A_{00-0,0,0}) = B_{00-0,0,2}/B_{00-0,0,0}$

For an arbitrary secondary pad configuration, the relative corrections for each attenuator are combined. The relative secondary pad corrections can be modeled over the 0-to-100-kHz frequency span as a magnitude offset and a phase ramp. With this simplification, secondary pad calibration data can be measured at one frequency using the HP 3562A's built-in sine source. The combined secondary pad correction is then a magnitude-offset/phase-ramp adjustment to the primary pad correction. The resultant correction curve produces channel-to-channel match accuracy of  $\pm 0.1$  dB and  $\pm 0.5$  degree.

#### Acknowledgments

The HP 3562A is the end result of an extensive project that started at HP's Santa Clara Division and culminated at Lake Stevens Instrument Division. We would like to acknowledge those contributors at Santa Clara Division: Webb McKinney, Terry Donahue, Dick Fowles, and Don Langdon provided direction during the early phases of the project. Jim Dunlay, Al Gee, Al Helgelson, Chuck Lowe, and Doug White contributed to the initial hardware design. Barbara Grote, Lani Maragay, and Mary Ryan contributed to the initial software design. At Lake Stevens Instrument Division, many others made important contributions toward the project completion. Those designers who contributed during release to production were John Elm, switching power supply, Alan Henshaw, mechanical design, Jan Hofland, digital filter assembly, Larry Sanders, analog-to-dig-

|                 | B <sub>00</sub>                  | <b>B</b> <sub>20</sub>           | B <sub>40</sub>                  |

|-----------------|----------------------------------|----------------------------------|----------------------------------|

| A <sub>00</sub> | B <sub>00</sub> /A <sub>00</sub> | B <sub>20</sub> /A <sub>00</sub> | B <sub>40</sub> /A <sub>00</sub> |

| A <sub>20</sub> | B <sub>00</sub> /A <sub>20</sub> | $B_{20}/A_{20}$                  | B <sub>40</sub> /A <sub>20</sub> |

| A <sub>40</sub> |                                  | $B_{20}/A_{40}$                  |                                  |

**Fig. 10.** Single-channel and cross-channel primary attenuator pad correction curve variations.  $B_{40}$  represents the reciprocal of the frequency response of Channel 2 with the -40-dB pad engaged.  $B_{40}/A_{20}$  represents the correction curve for a cross-channel measurement with primary attenuator pads specified for each channel (40 dB in Channel 2, 20 dB in Channel 1). The six shaded values are stored in the HP 3562A and the other nine values are derived from the stored values.

ital converter, and Dave Shoup, local oscillator and trigger.

Bryan Murray implemented much of the display and synthesis software. Marty Bender implemented the diagnostics software, Praful Bhansali contributed to the demodulation software, and Peter Pias contributed to the waveform math software and FPP microcode. Frank Robey, Dave Rasmussen, Bill Brown, and Steve Kator contributed to automated testing.

Rick Kunin was the production engineer and Randy Eilert was the industrial designer. Larry Whatley was the program manager and Nick Pendergrass was one of the project managers. Also, Helen Chase and Sherry Clark provided key project support. Special thanks to all those involved in the final testing of the software and to the project teams' spouses for their understanding.

#### References

1. J.S. Epstein, et al, "Hardware Design for a Dynamic Signal Analyzer," *Hewlett-Packard Journal*, Vol. 35, no. 12, December 1984, pp. 12-17.

2. C.R. Panek and S.F. Kator, "Custom Digital Filters for Dynamic Signal Analysis," *ibid*, pp.28-36.

3. A.C. Shaw, The Logical Design of Operating Systems, Prentice-Hall, 1974.

4. G.R. Engel and D.R. Hiller, "Instrument Software for Dynamic Signal Analysis," *Hewlett-Packard Journal*, Vol. 35, no. 12, December 1984, pp. 17-19.

#### CORRECTION

In the December 1986 issue, the second language listed in Fig. 5 on page 7 should be Canadian *French*.

# Measurement Modes and Digital Demodulation for a Low-Frequency Analyzer

by Raymond C. Blackham, James A. Vasil, Edward S. Atkinson, and Ronald W. Potter

HE HP 3562A DYNAMIC SIGNAL ANALYZER provides three different measurement modes for lowfrequency spectrum and network analysis from 64  $\mu$ Hz to 100 kHz within one instrument with two input channels and a dynamic range of 80 dB:

Swept sine

Logarithmic resolution

FFT-based linear resolution.

These measurement modes use advanced digital signal processing algorithms to provide more accurate and more repeatable measurements than previously available with conventional analog circuit approaches.

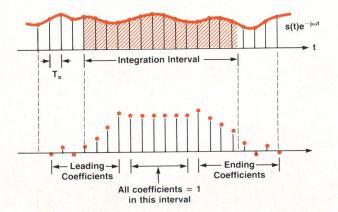

#### Swept Sine Mode

The swept sine measurement is based on the Fourier series representation of a periodic signal. Consider a stimulus signal:

$$s(t) = \sum_{n=-\infty}^{\infty} c_n e^{j\omega nt}$$

applied to the device under test (DUT) and a response signal:

$$\mathbf{r}(t) = \sum_{n=-\infty}^{\infty} d_n e^{j\omega nt}$$

where  $c_i$  and  $d_i$  are complex numbers, and  $c_i = c_{-i}^*$  and  $d_i = d_{-i}^*$  so that s(t) and r(t) are real signals. Ideally, s(t) is a perfect sine wave with perhaps a dc offset, or  $c_n = 0$  for n > 1. The frequency response of the DUT at frequency  $f = \omega/2\pi$  Hz is defined to be  $d_1/c_1$ . The swept sine measurement is a series of measurements of  $d_1$  and  $c_1$  for different frequencies.

The HP 3562A assumes that s(t) is connected to its Channel 1 input and r(t) is connected to its Channel 2 input.  $c_1$ is calculated using the standard Fourier series integral:

$$c_1 = \frac{1}{T} \int_0^T s(t) e^{-j\omega t} \, dt$$

where T =  $2\pi/\omega = 1/f$ . d<sub>1</sub> is calculated in the same way using r(t) in place of s(t).

The HP 3562A carries out this calculation on both input signals as follows (given for s(t) only):

1. The signal is sampled at intervals of  $T_s = 1/f_s$ , with  $f_s$ = the sample frequency. Let  $s_n = s(nT_s)$  for n = 0, 1, 2, ... 2.  $s_{\rm n}$  is multiplied by  $e^{-j\omega n}$  in real time using a digital local oscillator.

3. Samples spanning the time  $(N+19)T_s$ , where N is a positive integer, are used in a numerical integration algorithm to calculate an approximation to:

$$\frac{1}{MT}\int_0^{MT} s(t)e^{-j\omega t}\,dt$$

where M is a positive integer,  $MT \le (user-entered integration time) \le M(T+1)$ , and  $(N-1)T_s \le MT \le NT_s$ .

4.  $|c_1|^2$ ,  $|d_1|^2$ , and  $d_1c_1^*$  (the trispectrum) are calculated.

5. Steps 3 and 4 are repeated the number of times specified by the user-entered number of averages.

6. The values of  $|c_1|^2$  thus calculated are averaged together and stored. The same is done for  $|d_1|^2$  and  $d_1c_1^*$  (trispectrum average).

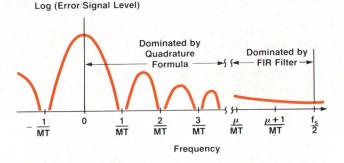

Integration Algorithm. Since:

$$\int_0^T e^{j\omega(n-1)t} dt = \begin{cases} T & \text{for } n = 1 \\ 0 & \text{for } n \neq 1 \end{cases}$$

we can simplify:

$$\begin{split} \frac{1}{T} \int_0^T s(t) e^{-j\omega t} dt &= \frac{1}{T} \int_0^T e^{-j\omega t} \left( \sum_{n=-\infty}^{\infty} c_n e^{j\omega n t} \right) dt \\ &= \frac{1}{T} \sum_{n=-\infty}^{\infty} c_n \int_0^T e^{j\omega (n-1)t} dt \end{split}$$

and we obtain:

$$\frac{1}{T}\int_0^T e^{-j\omega t} s(t)dt = c_1$$

as desired.